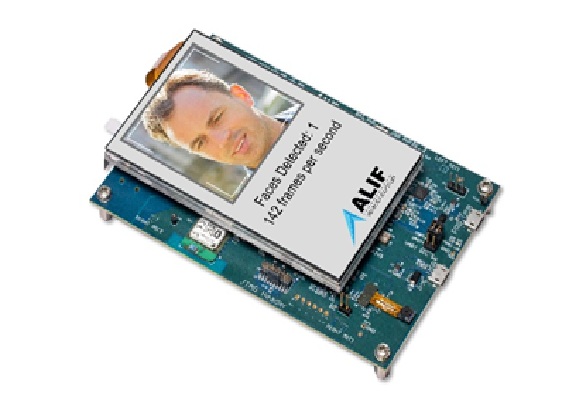

Alif Semiconductor est une société spécialisée dans le développement de microcontrôleurs et de processeurs de nouvelle génération, conçus pour intégrer l’intelligence artificielle et l’IoT de point terminal. Fondée en 2019, elle s’est imposée comme un acteur pionnier en proposant des architectures hybrides associant CPU et NPU.

Introduction : quand l’IA redéfinit les microcontrôleurs

Les microcontrôleurs (MCU) sont depuis longtemps au cœur des systèmes embarqués, exécutant des fonctions de contrôle simples et efficaces. Mais l’essor des applications d’intelligence artificielle (IA) sur le point terminal – appareils portables, capteurs intelligents, objets connectés – bouleverse les critères de conception. Désormais, la performance d’un MCU ne se limite plus à sa capacité de calcul traditionnelle : il doit aussi intégrer des fonctions avancées d’apprentissage automatique (ML) et d’inférence locale, tout en maîtrisant consommation énergétique et coûts.

Nouvelles exigences : du CPU seul au couple CPU/NPU

Pendant des décennies, les fabricants ont optimisé les MCU en renforçant leur cœur de calcul central (CPU). Mais l’exécution de charges de travail IA sur ces architectures reste limitée : un CPU seul, même performant, peine à traiter efficacement les opérations massivement parallèles des réseaux neuronaux. D’où l’émergence de solutions hybrides intégrant un coprocesseur neuronal (NPU). Ce dernier est spécialement conçu pour accélérer les opérations de multiplication-accumulation (MAC), fondamentales en ML, et réduire drastiquement les temps de réponse ainsi que la consommation énergétique.

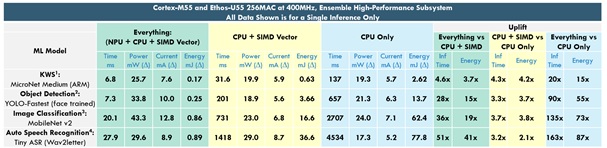

Les comparatifs de performances illustrent l’écart : un MCU de dernière génération associant CPU vectoriel (Cortex-M55 avec extension SIMD Helium) et NPU (Ethos-U55) peut multiplier par plusieurs dizaines – voire centaines – l’efficacité énergétique et la rapidité des inférences par rapport à un CPU seul. Cette architecture redéfinit les perspectives pour des applications comme la reconnaissance vocale, la détection de présence, la classification d’images ou l’analyse de signaux biométriques.

Optimiser la mémoire et l’efficacité énergétique

Au-delà de la puissance de calcul, l’architecture mémoire joue un rôle décisif. Le déplacement des données consomme souvent plus d’énergie que leur traitement. Une topologie mémoire optimisée – combinant mémoires rapides à faible latence pour les tenseurs et mémoires massives embarquées pour les flux de capteurs – permet de réduire les goulets d’étranglement et d’éviter le recours coûteux à des mémoires externes, plus énergivores et moins sûres.

L’autre enjeu majeur reste l’autonomie des batteries. Pour les appareils portables (lunettes intelligentes, montres, capteurs de santé), l’IA locale doit fonctionner sur de petites batteries sans compromis sur la réactivité. Les approches modernes intègrent :

- des sous-systèmes basse consommation capables de rester actifs en permanence,

- des régions haute performance activées uniquement à la demande,

- une gestion fine de l’alimentation (jusqu’à une douzaine de domaines indépendants) pilotée dynamiquement par le système.

Cette orchestration intelligente garantit un équilibre entre puissance de calcul et sobriété énergétique.

Un enjeu de productivité pour les développeurs

L’intégration de l’IA embarquée ne doit pas se traduire par une complexité insurmontable pour les ingénieurs. La compatibilité des NPU Ethos avec l’écosystème Arm Cortex-M facilite la transition. Les développeurs peuvent continuer à utiliser leurs environnements familiers, tout en exploitant de nouveaux outils de compilation qui répartissent automatiquement les charges de travail entre CPU et NPU.

Cet alignement réduit la courbe d’apprentissage et évite la fragmentation technologique. Par ailleurs, le support continu d’Arm garantit une compatibilité avec les frameworks de ML les plus répandus, tels que TensorFlow Lite, élargissant ainsi le champ d’innovation.

Vers des MCU hybrides de nouvelle génération

L’évolution vers des MCU hybrides CPU/NPU est inévitable. Elle s’inscrit dans la continuité des grandes étapes qui ont marqué l’histoire des microcontrôleurs : mémoire Flash intégrée, connectivité USB, et aujourd’hui IA locale. Cette tendance prépare l’arrivée de modèles encore plus puissants, capables de gérer des architectures de ML basées sur les transformateurs et d’adresser les usages émergents de l’IA générative au plus près du capteur. Les fabricants qui anticipent cette mutation contribuent à redéfinir la frontière entre cloud et edge computing, en rapprochant l’intelligence des données.

Conclusion : une nouvelle ère pour les systèmes embarqués

Les microcontrôleurs entrent dans une phase de transformation profonde. L’intégration de l’IA sur le point terminal ouvre la voie à des objets plus intelligents, réactifs et économes en énergie. Pour les concepteurs de systèmes, la clé réside dans le choix d’architectures équilibrées, où CPU, NPU et mémoire interagissent harmonieusement.

Cette évolution façonnera les prochaines générations de produits électroniques, de la santé connectée aux objets portables, en passant par l’industrie et les transports.

L’article complet est disponible en téléchargement sur cette page.

La mission de PEI est de fournir à ses lecteurs des informations sur les nouveaux produits et services liés au secteur de l'industrie et qui sont disponibles sur le marché français.

La mission de PEI est de fournir à ses lecteurs des informations sur les nouveaux produits et services liés au secteur de l'industrie et qui sont disponibles sur le marché français.